# 7. Circuits Numériques Logique

Initiation à l'électronique

JEAN-MICHEL SALLESE

# CIRCUITS NUMÉRIQUES

Traitement numérique des signaux

Système binaire et logique binaire

Opérateurs logiques et algèbre de Boole

Systèmes logiques combinatoires

Elément de mémoire et bascule

Systèmes logiques séquentiels

## MONDE ANALOGIQUE

#### GRANDEURS À VARIATION CONTINUE

Un continum de valeurs possibles dans un intervalle donné

Exemples: force, position, température tension, courant, puissance

Traitement analogique

Amplifier, filtrer, déformer, additionner, soustraire

MONDE NUMÉRIQUE

GRANDEURS À VALEURS DISCRÈTES

Un nombre fini de valeurs possibles pouvant être codées avec des symboles

> Exemples: nombre d'objets états discrets d'un ensemble

> > Traitement numérique

Calculs, opérations logiques

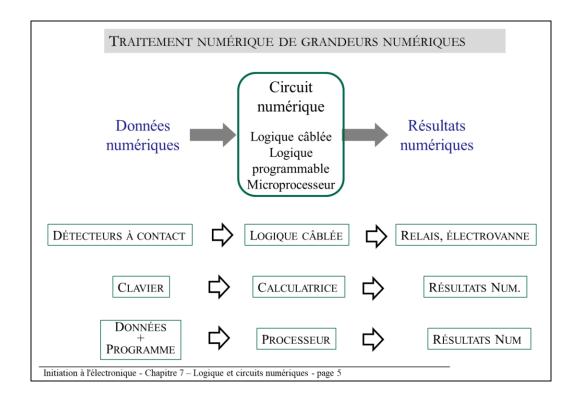

De nombreux systèmes sont entièrement numériques.

Leurs données sont d'origine numériques, et les résultats sont directement utilisés sous cette forme numérique.

Ces résultats peuvent également servir de données numériques.

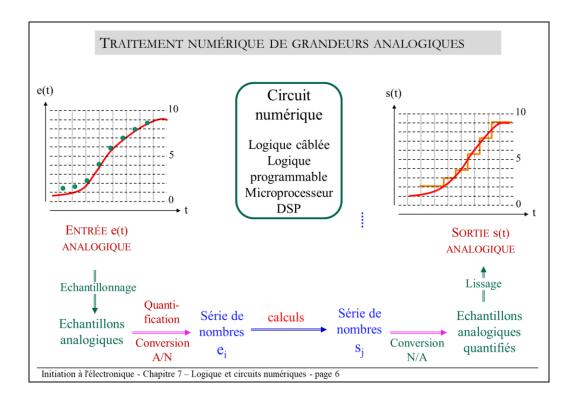

L'électronique numérique est aussi très largement utilisée dans le traitement de grandeurs analogiques.

Grace à la rapidité d'exécution des calcul par les processeurs, elle peut remplacer une partie des circuits analogiques traditionnels.

Pour cela, il faut pouvoir convertir des variables analogiques continues en variables numériques discrète grâce à des convertisseurs A/N, analogique-numérique.

De même, pour 'revenir' aux signaux analogiques après que les calculs aient été effectué, il faut pouvoir convertir des signaux numériques en grandeurs analogiques (tensions ou courants).

C'est ce que réalisent les convertisseurs N/A, numérique-analogiques.

#### AVANTAGES ET INCONVÉNIENTS DU TRAITEMENT NUMÉRIQUE

### **Avantages**

Insensibilité au bruit: tant que l'on peut identifier les chiffres

Précision: limitée uniquement par le nombre de chiffres calculés

Souplesse: toute fonction que l'on peut mettre en équation ou tabuler

#### Inconvénients

Conversion A/N et N/A: limites en termes de précision et de vitesse

Complexité: nombre élevé de composants et de connections

Temps de traitement: un calcul, même simple, peut nécessiter beaucoup

d'opérations, donc un temps important

Ces inconvénients sont minimisés par l'augmentation des performances (densité, vitesse, précision) des circuits intégrés

Initiation à l'électronique - Chapitre 7 - Logique et circuits numériques - page 7

L'hégémonie des circuits numériques est due aux progrès constants des techniques d'intégration qui permettent de réaliser des circuits intégrés de plus en plus complexes et rapides avec un coût par fonction qui ne cesse de diminuer.

## Système binaire

Chiffre (Bit):

$$a_i = [1, 0]$$

Représentation d'un nombre en base 2 :  $a_{n-1} a_{n-2} \dots a_2 a_1 a_0$ MSB LSB

valeur:

$$A = \sum_{i=0}^{i=n-1} a_i \cdot 2^i$$

## **Exemple**

notation binaire: 10011

valeur décimale:

$$A = 1 \cdot 2^4 + 0 \cdot 2^3 + 0 \cdot 2^2 + 1 \cdot 2^1 + 1 \cdot 2^0$$

=  $1 \cdot 16 + 0 \cdot 8 + 0 \cdot 4 + 1 \cdot 2 + 1 \cdot 1$

= 19

Initiation à l'électronique - Chapitre 7 - Logique et circuits numériques - page 9

MSB = Most Significant Bit = le bit de poids le plus fort (2<sup>n-1</sup>)

LSB = Least Significant Bit = le bit de poids le plus faible (20)

## LOGIQUE BINAIRE

Une variable binaire ne peut avoir que deux valeurs appelées aussi *Etats*

| Vrai 1            | 5 Volts - High           | Close                    |

|-------------------|--------------------------|--------------------------|

| Faux 0            | 0 Volt - Low             | Open                     |

| Valeur<br>logique | EQUIVALENT<br>ÉLECTRIQUE | EQUIVALENT<br>ÉLECTRIQUE |

Initiation à l'électronique - Chapitre 7 – Logique et circuits numériques - page 10

A quelques rares exceptions près, les circuits électroniques numériques représentent le "0" logique par une tension quasi nulle par rapport à la masse (référence 0 V), et le "1" logique par une tension positive, généralement proche de la tension d'alimentation, par rapport à la masse (référence 0 V).

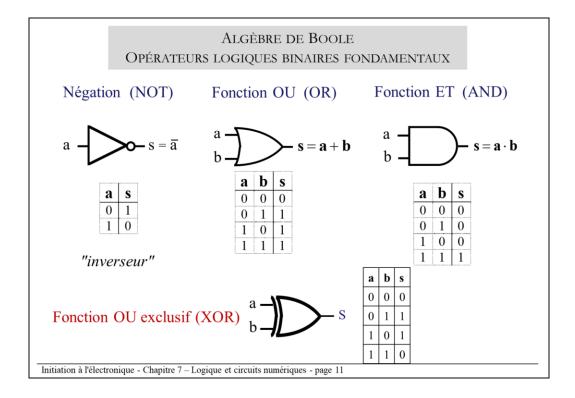

**Négation**, aussi appelée **inversion**, notée — ou parfois / La sortie est l'opposé (ou complément) de l'entrée.

OU, notée +

Il suffit que l'une des entrées soit vraie pour que la sortie soit vraie.

ET, notée · ou \* ou encore &

Il est nécessaire que toutes les entrées soient vraies pour que la sortie soit vraie.

Il est important de ne pas confondre les notations + et  $\cdot$  logiques avec l'addition et la multiplication des nombres, même si, en algèbre de Boole, on utilise parfois les termes "somme" et "produit" sous-entendu "logique" .

La table de vérité d'une fonction logique à n variables est un tableau listant le résultat correspondant à chacune des 2<sup>n</sup> combinaisons possibles des n variables d'entrée.

#### RÈGLES DE L'ALGÈBRE DE BOOLE

$$\overline{\overline{a}} = a$$

$a \cdot 0 = 0$   $a + 0 = a$   $a \cdot 1 = a$   $a + 1 = 1$   $a \cdot a = a$   $a + a = a$   $a \cdot \overline{a} = 0$   $a + \overline{a} = 1$

Commutativité

$$a \cdot b = b \cdot a$$

$a + b = b + a$

Distributivité

$$a \cdot (b+c) = (a \cdot b) + (a \cdot c)$$

$a+(b \cdot c) = (a+b) \cdot (a+c)$

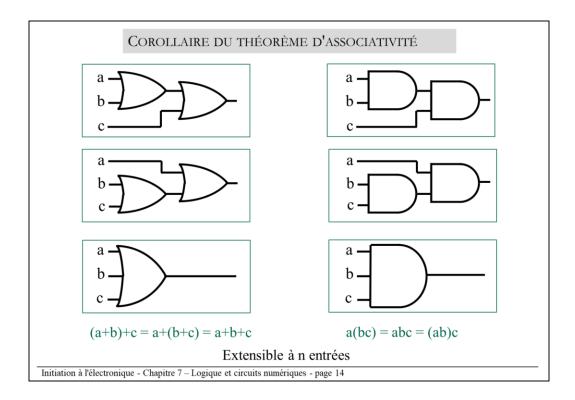

Associativité

$$a \cdot (b \cdot c) = (a \cdot b) \cdot c = a \cdot b \cdot c$$

$a + (b + c) = (a + b) + c = a + b + c$

Consensus

$$(a \cdot c) + (b \cdot \overline{c}) + (a \cdot b) = (a \cdot c) + (b \cdot c)$$

$$(a+c)\cdot(b+\overline{c})\cdot(a+b) = (a+c)\cdot(b+c)$$

$a+(a\cdot b) = a$   $a+(\overline{a}\cdot b) = a+b$

Loi De Morgan

$$\overline{a \cdot b} = \overline{a} + \overline{b}$$

$\overline{a + b} = \overline{a \cdot b}$

#### Démonstration en établissant la table de vérité de chaque terme

Initiation à l'électronique - Chapitre 7 - Logique et circuits numériques - page 12

La loi de Morgan est utile pour simplifier (factoriser) l'architecture de circuits numériques, ce qui revient à réduire le nombre de portes logiques utilisées pour réaliser une fonction.

# Démonstration du théorème de De Morgan

| a | b | a+b | ā∙b | ā | $\bar{\mathbf{b}}$ |

|---|---|-----|-----|---|--------------------|

| 0 | 0 | 1   | 1   | 1 | 1                  |

| 0 | 1 | 0   | 0   | 1 | 0                  |

| 1 | 0 | 0   | 0   | 0 | 1                  |

| 1 | 1 | 0   | 0   | 0 | 0                  |

$$\overline{a+b} = \overline{a} \cdot \overline{b}$$

| a | b | a·b | ā+b | ā | b |

|---|---|-----|-----|---|---|

| 0 | 0 | 1   | 1   | 1 | 1 |

| 0 | 1 | 1   | 1   | 1 | 0 |

| 1 | 0 | 1   | 1   | 0 | 1 |

| 1 | 1 | 0   | 0   | 0 | 0 |

$$\overline{a \cdot b} = \overline{a} + \overline{b}$$

# Démonstration du théorème de distributivité

| a | b | c | b+c | a·b | a·c | a· (b+c) | (a·b)+(a·c |

|---|---|---|-----|-----|-----|----------|------------|

| 0 | 0 | 0 | 0   | 0   | 0   | 0        | 0          |

| 0 | 0 | 1 | 1   | 0   | 0   | 0        | 0          |

| 0 | 1 | 0 | 1   | 0   | 0   | 0        | 0          |

| 0 | 1 | 1 | 1   | 0   | 0   | 0        | 0          |

| 1 | 0 | 0 | 0   | 0   | 0   | 0        | 0          |

| 1 | 0 | 1 | 1   | 0   | 1   | 1        | 1          |

| 1 | 1 | 0 | 1   | 1   | 0   | 1        | 1          |

| 1 | 1 | 1 | 1   | 1   | 1   | 1        | 1          |

| a | b | c | p.c | a+b | a+c | a+(b·c) | (a+b)·(a+c) |

|---|---|---|-----|-----|-----|---------|-------------|

| 0 | 0 | 0 | 0   | 0   | 0   | 0       | 0           |

| 0 | 0 | 1 | 0   | 0   | 1   | 0       | 0           |

| 0 | 1 | 0 | 0   | 1   | 0   | 0       | 0           |

| 0 | 1 | 1 | 1   | 1   | 1   | 1       | 1           |

| 1 | 0 | 0 | 0   | 1   | 1   | 1       | 1           |

| 1 | 0 | 1 | 0   | 1   | 1   | 1       | 1           |

| 1 | 1 | 0 | 0   | 1   | 1   | 1       | 1           |

| 1 | 1 | 1 | 1   | 1   | 1   | 1       | 1           |

$a \cdot (b+c) = (a \cdot b) + (a \cdot c)$

$a+(b\cdot c)=(a+b)\cdot (a+c)$

La définition des fonctions logiques OU et ET reste valable pour un nombre quelconque d'entrées.

Des réalisations physiques sous forme de circuits intégrés standards sont disponibles avec 2, 3, 4 et 8 entrées.

Les circuits logiques programmables offrent encore plus de souplesse.

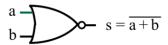

# OPÉRATEURS LOGIQUES UNIVERSELS

# Fonction NOT-OR (NOR)

# Fonction NOT-AND (NAND)

| a | b | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

| a | b | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Le 'o' de sortie symbolise la négation

Ces opérateurs sont simples à réaliser avec des composants électroniques

Initiation à l'électronique - Chapitre 7 - Logique et circuits numériques - page 15

En circuits intégrés standards du commerce, les portes NAND et NOR sont disponibles avec 2, 3, 4 et 8 entrées.

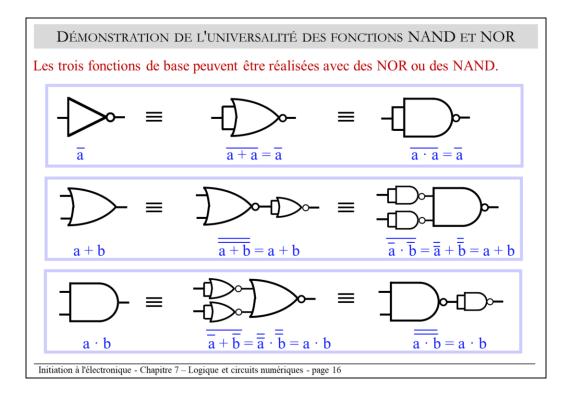

Avec uniquement des opérateurs NOR, respectivement NAND, on peut réaliser les trois fonctions de base, et donc toute fonction logique.

De même, on peut faire la fonction NOR avec uniquement des fonctions NAND, et des fonctions NAND avec uniquement des fonctions NOR.

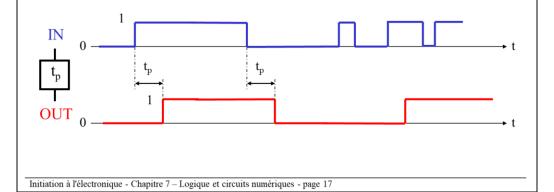

### DYNAMIQUE DES OPÉRATEURS LOGIQUES

Le temps de réaction d'un opérateur logique est modélisé par un élément de retard à la sortie de l'opérateur idéal (NOT, ET, OU, NAND, NOR).

Il introduit un temps de propagation  $t_p$  entre un changement d'état de sa sortie vis-à-vis de son entrée.

Un intervalle de temps inférieur à t<sub>p</sub> n'aura aucun effet sur la sortie.

Ce comportement de l'élément de retard modélise le fait qu'un opérateur réel a une limite interne en terme de temps de réaction.

Lorsque les signaux changent rapidement d'état, par ex. en quelques centaines ou dizaines de nanosecondes, voire moins, le retard intrinsèque aux circuits numériques doit être pris en compte pour des questions de synchronisation.

Les simulateurs électriques intègre cette donnée.

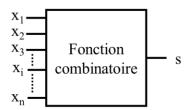

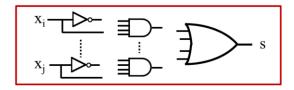

### FONCTION LOGIQUE COMBINATOIRE QUELCONQUE

A chacune des 2<sup>n</sup> combinaisons des entrées x<sub>i</sub> correspond une valeur de sortie

Toute fonction combinatoire peut être décomposée en une "somme" (OR) de "produits" (AND) des entrées ou de leurs inverses (NOT).

Initiation à l'électronique - Chapitre 7 - Logique et circuits numériques - page 19

Dans un système dit 'combinatoire, une suite donnée de variables d'entrée donnera toujours le même résultat en sortie.

Le signal de sortie ne dépend donc pas des signaux passés.

Bien que dans les cas simples, la synthèse et la réalisation peuvent se faire manuellement, on utilise des programmes spécialisés de synthèse et de simulation.

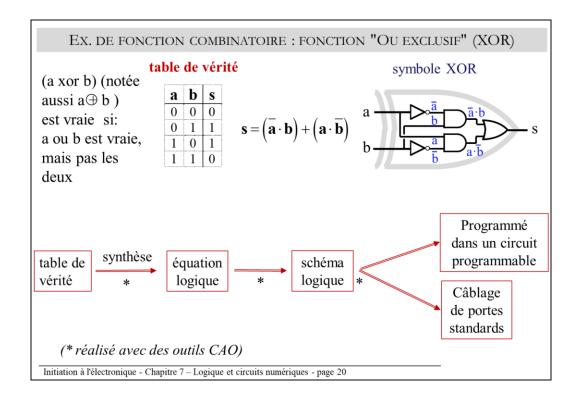

Les réalisations en logique câblée avec des circuits standards ne sont possibles que pour des cas relativement simples. C'est le cas de la fonction XOR qui est si utile qu'elle est considérée comme une fonction de base, avec un symbole spécifique, et disponible en circuit standard.

Actuellement les fonctions logiques sont généralement réalisées avec des circuits programmables tels que des FPGA (Field Programmable Gate Array).

Une autre solution serait d'utiliser un microcontrôleur et d'y implanter un programme qui effectue l'opération logique. Tous les microcontrôleurs ont dans leur jeu d'instructions les fonctions AND, OR, NOT et XOR.

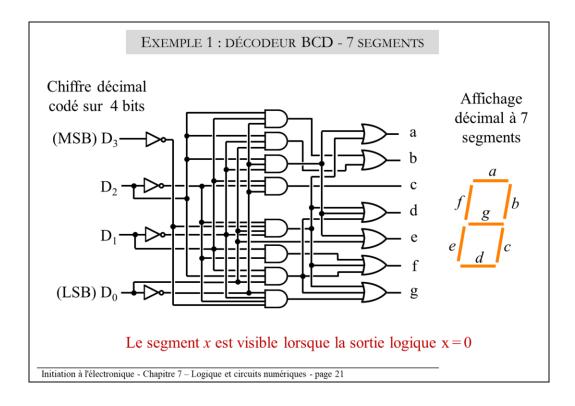

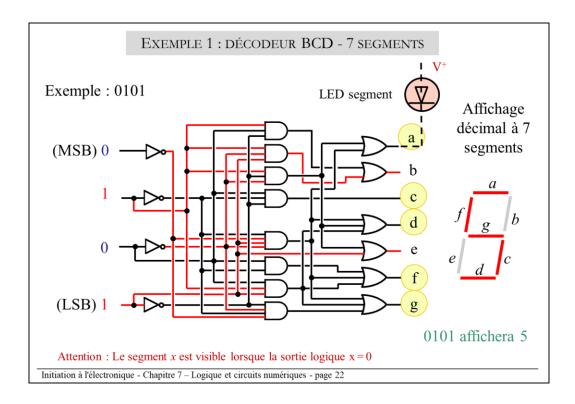

En code BCD les chiffres décimaux 0 à 9 sont codés en binaire. Ce code est souvent utilisé lorsqu'un nombre doit être affiché sous une forme décimale.

L'exemple ci-dessus donne le schéma d'un décodeur qui va faire apparaître les segments représentant le chiffre qui correspond au code binaire appliqué à l'entrée.

Chaque sortie de  ${\bf a}$  à  ${\bf g}$  est une fonction combinatoire des entrée  $D_0$  à  $D_3$

Exemple du décodage du nombre binaire 101, qui est 5 en base 10.

En rouge sont les 'signaux' au potentiel  $V^{\scriptscriptstyle +}$ , et en noir 0V.

Attention: ici les LED s'allument si on applique 0V aux sorties du décodeur.

# EXEMPLE 1 : DÉCODEUR BCD - 7 SEGMENTS

|            |    |    |    | 1 |   |   |   |   |   |   |         |

|------------|----|----|----|---|---|---|---|---|---|---|---------|

| <b>D</b> 3 | D2 | D1 | Do | a | b | c | d | e | f | g | display |

| 0          | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1 |         |

| 0          | 0  | 0  | 1  | 1 | 0 | 0 | 1 | 1 | 1 | 1 | I       |

| 0          | 0  | 1  | 0  | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 2       |

| 0          | 0  | 1  | 1  | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 3       |

| 0          | 1  | 0  | 0  | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 4       |

| 0          | 1  | 0  | 1  | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 5       |

| 0          | 1  | 1  | 0  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 6       |

| 0          | 1  | 1  | 1  | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 7       |

| 1          | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | В       |

| 1          | 0  | 0  | 1  | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 9       |

|            |    |    |    | 1 |   |   |   |   |   |   |         |

$!: Les egment\ x\ appara \hat{i}t\ lorsque\ la\ sortie\ logique\ correspondante\ est\ \hat{a}\ 0$

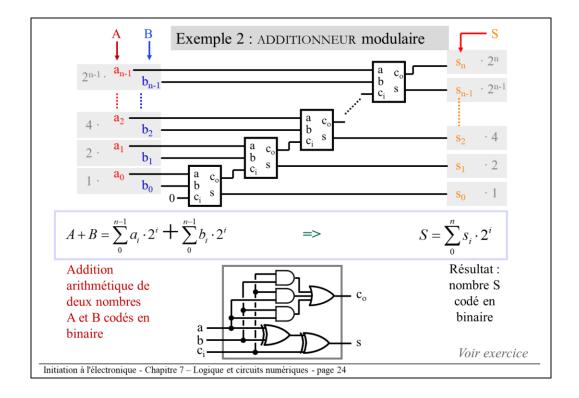

Pour faire l'addition de deux nombres en décimal:

$$\begin{array}{cccc} \text{retenue} & 1 & 1 \\ A & 1 & 6 & 5 & 3 \\ \underline{B} & 2 & 5 & 7 \\ \hline S & 1 & 9 & 1 & 0 \\ \end{array}$$

pour chaque puissance de dix (unités, dizaines, centaines, ...) on additionne les deux chiffres et l'éventuelle retenue de l'addition précédente, ce qui donne le chiffre de la somme et une éventuelle retenue pour l'addition suivante.

On peut faire la même chose avec deux nombres codés en binaire:

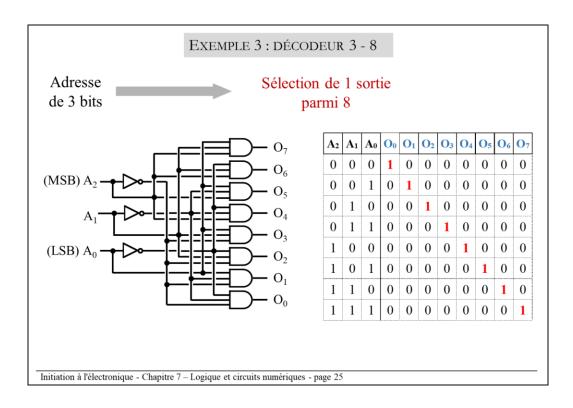

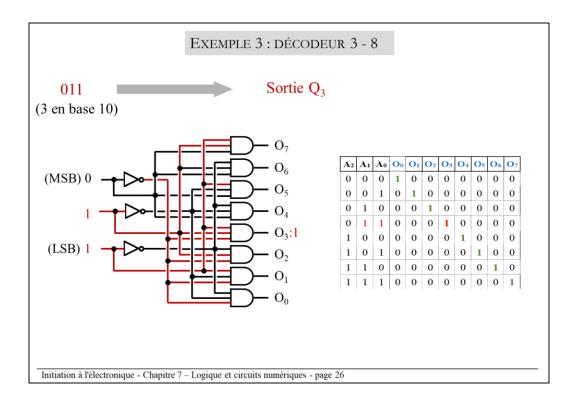

Ce décodeur active une seule des sorties numérotées de 0 à 7 en fonction de l'adresse codée en binaire à l'entrée via  $A_0$   $A_1$   $A_2$ .

$$s = 0$$

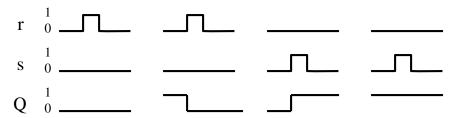

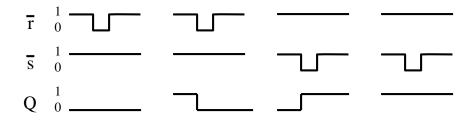

et  $r = 1$  $Q = 0$  $Q' = \overline{Q} = 1$  $Q$  est mis à  $0 \Leftrightarrow$  "reset" $s = 1$  et  $r = 0$  $Q' = 0$  $Q = \overline{Q}' = 1$  $Q$  est mis à  $1 \Leftrightarrow$  "set" $s = 0$  et  $r = 0$  $Q' = \overline{Q}$  $Q = \overline{Q}' = Q$ état stable, qu'il soit  $1$  ou  $0$  $s = 1$  et  $r = 1$  $Q = 0$  $Q' = 0 \neq \overline{Q}$ état à éviter  $!$

La bascule bistable, mise dans un état donné par activation de l'une des deux entrées set ou (exclusif) reset, conserve ensuite cet état tant que les entrées restent inactives.

Initiation à l'électronique - Chapitre 7 - Logique et circuits numériques - page 28

L'état d'entrée s=r=1 est en général interdit car, d'une part les deux sorties Q et Q' ne sont alors plus complémentaires, d'autre part et surtout si s et r reviennent à 0 simultanément il est impossible de prévoir l'état que prendra la sortie Q!

Si l'on respecte l'interdiction de l'état s=r=1, on peut rencontrer les quatre cas suivants:

Ce système est dit séquentiel et son comportement est fondamentalement différent de celui d'un système combinatoire puisque la même combinaison des entrées s et r (dans ce cas 0 et 0) peut donner des résultats différents en fonction des événement passés.

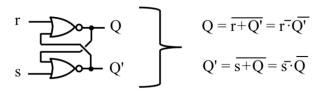

### RÉALISATION DE L'ÉLÉMENT DE MÉMOIRE SR

portes NOR

portes NAND

$$Q = \overline{P + Q'} = \overline{P \cdot Q'}$$

$$Q = \overline{P \cdot Q'} = \overline{P \cdot Q'}$$

$$\overline{Q} = \overline{P \cdot Q} = \overline{P \cdot Q}$$

$$\overline{Q} = \overline{P \cdot Q} = \overline{$$

### On passe d'un schéma à l'autre en appliquant le théorème de De Morgan

L'élément de mémoire réalisé avec des portes NAND est mis dans un état donné par un 0 sur l'une des entrées.

Les deux entrées ne doivent jamais être à 0 simultanément.

ELLE CONSERVE SON ÉTAT TANT QUE LES ENTRÉES RESTENT À 1.

Initiation à l'électronique - Chapitre 7 - Logique et circuits numériques - page 29

L'élément de mémoire réalisé avec des portes NAND est mis dans un état donné par un 0 sur l'une ou (exclusif) l'autre des entrées, elle conserve son état inchangé tant que les entrée restent inactives à 1. Les deux entrées ne doivent jamais être à 0 simultanément.

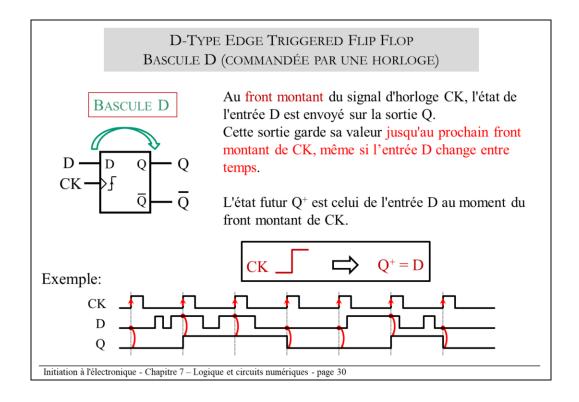

Seule la bascule D sera étudiée ici, car c'est la plus répandue, en particulier dans les circuits logiques programmables.

Mais il existe d'autre types de "Edge Triggered Flip Flop", en particulier la bascule JK.

Toute bascule d'un type donné peut être transformée en une bascule d'un autre type par ajout de logique combinatoire.

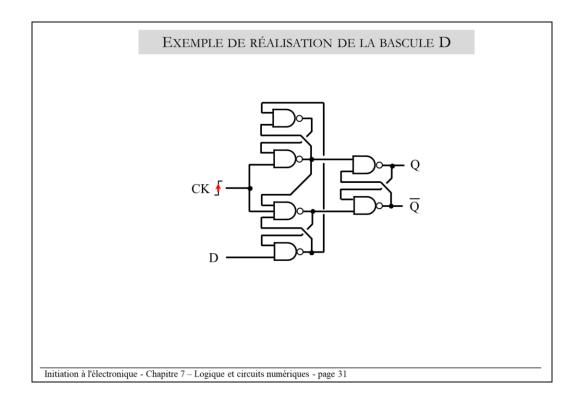

Ce schéma est donné à titre d'information pour montrer qu'une fonction aussi simple nécessite déjà 6 portes élémentaires, ce qui représente déjà une vingtaine de transistors en logique CMOS .

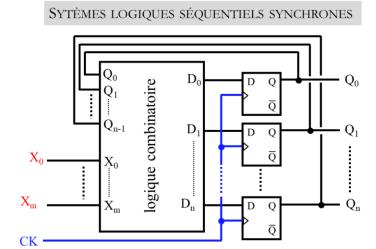

# SYSTÈMES LOGIQUES SÉQUENTIELS SYNCHRONES

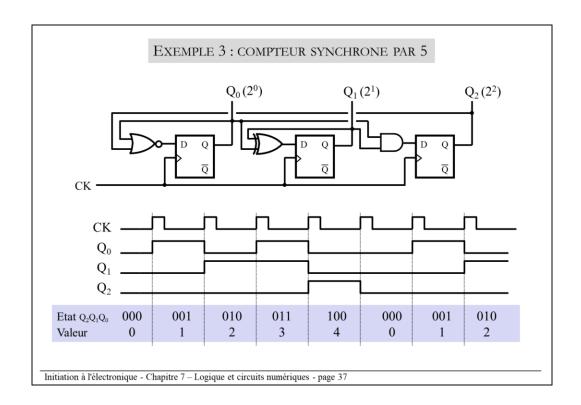

Juste après le front montant du signal d'horloge CK, chaque bascule prendra un nouvel état (dit futur)  $Q_i^+ = D_i$  qui est une fonction combinatoire des états présents de toutes les bascules  $Q_0$  à  $Q_n$  et de toutes les entrées  $X_0$  à  $X_m$  à l'instant du front d'horloge.

Initiation à l'électronique - Chapitre 7 - Logique et circuits numériques - page 33

Le système est dit synchrone car les bascules ont toutes le même signal d'horloge et ne peuvent donc changer d'état qu'en présence du front de cette horloge.

Par contre, le nouvel état de sortie  $Q^+_0...Q^+_n$  juste après le front montant de l'horloge sera fonction de l'état actuel  $Q_0...Q_n$  et aussi des entrées  $X_0...X_m$ .

Il s'agit d'un circuit synchrone.

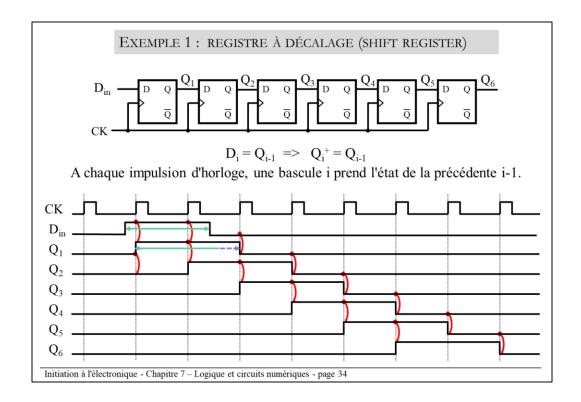

En reliant les bascules comme ci-dessus, et en appliquant le même signal d'horloge à toutes, on décale la valeur des entrée D à chaque signal d'horloge.

Plus précisément, la première bascule échantillonne l'entrée  $D_{\rm in}$  aux fronts montants de l'horloge

Cette information est ensuite transférée d'une bascule dans la suivante à chaque front montant de l'horloge.

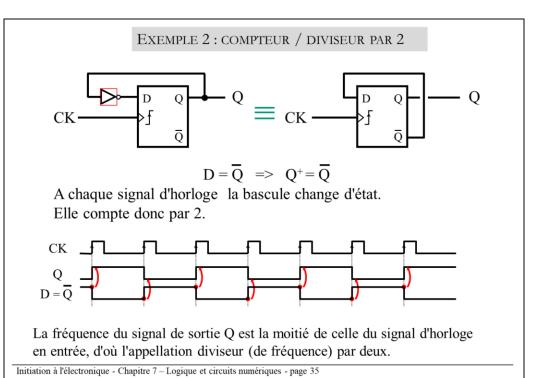

Le bouclage de la sortie NOT Q vers l'entrée D revient à diviser par 2 le nombre d'impulsions de l'horloge CK

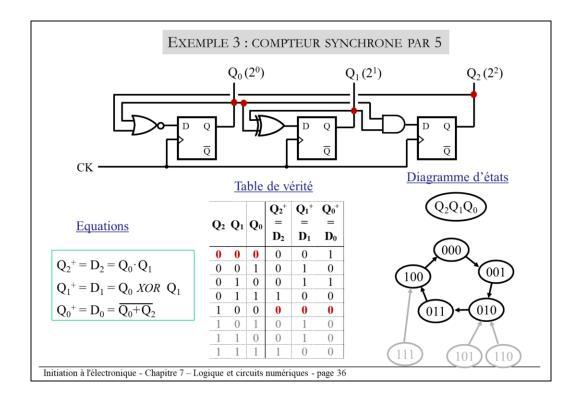

La méthode d'analyse consiste à:

- 1. Etablir l'équation de chaque  $D_i$ , donc de l'état futur  $Q_i^+$  pour chaque bascule en fonction de tous les  $Q_i$ .

- 2. Etablir la table de vérité de l'état futur du système pour tous les états présents possibles (toutes les combinaisons possibles de tous les Q<sub>i</sub>).

- 3. En partant de l'état initial, établir s'enchaînent tous les états possibles du systèmes (le diagramme d'état) en utilisant la table de vérité.

- Ou/et construire le chronogramme de la page précédente qui représente l'évolution temporelle des états de chaque bascule.

Dans cet exemple les états 5 (101), 6 (110) et 7 (111) n'apparaissent jamais en fonctionnement normal. Toutefois l'un d'eux peut apparaître lors de l'enclenchement ou suite à un parasite; il est alors important de vérifier que le système retourne dans son cycle normal et ne reste pas piégé dans un cycle parasite.

On voit qu'en an attribuant un poids  $2^i$  à chaque bit  $Q_i$ , l'état du compteur représentera le nombre binaire correspondant :

$$Valeur = \sum_{0}^{n-1} b_i 2^i$$

Le circuit compte jusqu'à 4, mais au 'cinquième 'CK' il va maintenir  $Q_0$  à 0 (au lieu de transiter ver '1') et remettre  $Q_2$  à '0' (tandis qu'il était à '1'). L'état des sorties sera donc 0, 0, 0.

##

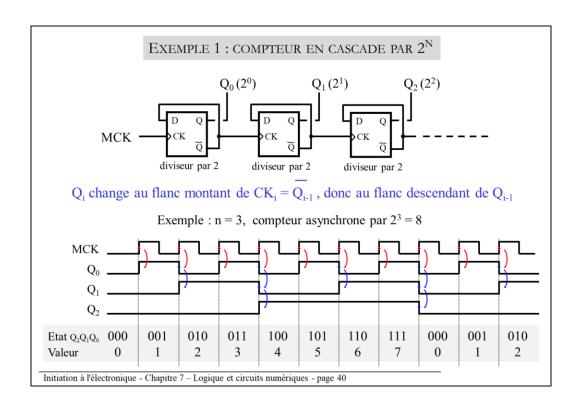

Chaque bascule peut avoir son propre signal d'horloge, ou elle peut être forcée à 1 (Set) ou à 0 (Reset) à tout instant autre qu'au front de son horloge. Les bascules ne sont donc pas synchrones.

Initiation à l'électronique - Chapitre 7 - Logique et circuits numériques - page 39

Dans ce système la logique combinatoire génère le signal d'horloge de chaque bascule à partir d'une horloge maître MCK combinées avec des entrées  $X_j$  et des sorties  $Q_i$ . Souvent la logique combinatoire peut aussi forcer l'état de chaque bascule à tout instant par des commandes supplémentaires Set et Reset. Le système est dit asynchrone car les bascules ne sont plus synchronisées sur le même front d'horloge.

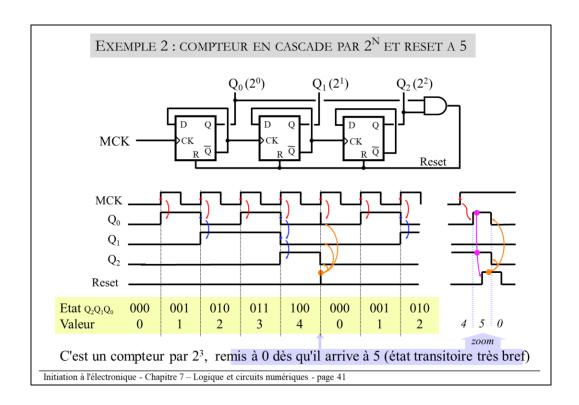

Chaque bascule divise par deux la fréquence de son horloge. Comme la sortie d'un diviseur est l'horloge du diviseur suivant, le facteur de division total est donc de  $2^{\text{nb de bascules}}$ .

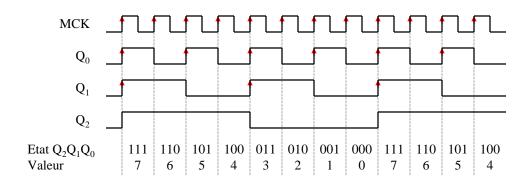

On utilise  $\overline{la}$  sortie Q de chaque diviseur comme horloge du suivant, ce qui correspond à déclencher la bascule i au front descendant de  $Q_{i-1}$ . Ceci est nécessaire pour que la valeur correspondant à l'état du système aille en croissant. On peut vérifier facilement qui si chaque diviseur i est commandé par le front montant de  $Q_{i-1}$  on obtient un compte à rebours (down counter).

Si le compteur est remis quasi instantanément à 0 dès qu'il atteint la valeur m, il va passer par les états :  $0, 1, 2, \ldots, m-2, m-1, ('m'n'est pas atteint), 0, 1, 2, \ldots$ , ce qui correspond à un compteur par m. Il faut que le compteur original soit de modulo supérieur à m. Le plus simple est de prendre un compteur asynchrone par  $2^n \ge m$ .

Avec ce principe, on fait facilement un compteur par n'importe quel nombre.

#### SYNCHRONE VERSUS ASYNCHRONE

## Synchrones

- Temps de propagation du front d'horloge identique pour toutes les bascules: synchronisation des entrées

- Optimum pour la rapidité

- Mais système combinatoire qui peut s'avérer complexe (nombre de combinaisons possibles: 2<sup>nb</sup> de bascules)

## Asynchrones

- Temps de propagation variable d'une entrée, augmente avec le nombre de transitions à réaliser.

- Risques d'états transitoires parasites

- Permet de minimiser la complexité du système combinatoire associé

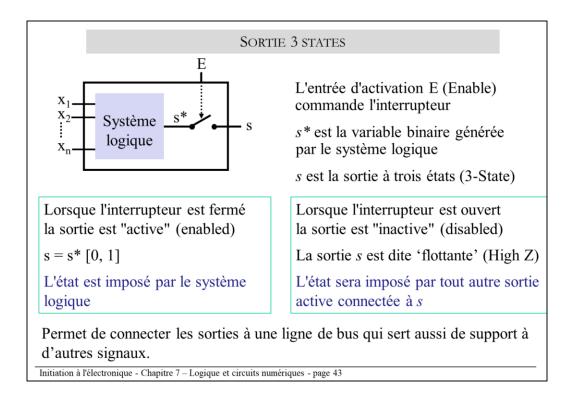

Les sorties 3-state (ou three-state) sont souvent représentées par: